INTERFACING

the

3333

MICROCOMPUTER

Brian Bannister Michael Whitehead Interfacing the BBC Microcomputer

# General Editor: Ian Birnbaum (General Adviser (Microelectronics in Education) Education Department, Humberside County Council)

Advanced Graphics with the Acorn Electron

Ian O. Angell and Brian J. Jones

Advanced Graphics with the BBC Model B Microcomputer

Ian O. Angell and Brian J. Jones

Interfacing the BBC Microcomputer

Brian Bannister and Michael Whitehead

Assembly Language Programming for the Acorn Electron

Ian Birnbaum

Assembly Language Programming for the BBC Microcomputer (second edition)

Ian Birnbaum

Using Your Home Computer (Practical Projects for the Micro Owner)

Garth W. P. Davies

Beginning BASIC with the ZX Spectrum

Judith Miller

Using Sound and Speech on the BBC Microcomputer

Martin Phillips

#### Other books of related interest

Advanced Graphics with the IBM Personal Computer

Ian O. Angell

Programming in Z80 Assembly Language

Roger Hutty

# Interfacing the BBC Microcomputer

Brian Bannister Michael Whitehead

### © Brian Bannister and Michael Whitehead 1985

All rights reserved. No reproduction, copy or transmission of this publication may be made without written permission.

No paragraph of this publication may be reproduced, copied or transmitted save with written permission or in accordance with the provisions of the Copyright Act 1956 (as amended).

Any person who does any unauthorised act in relation to this publication may be liable to criminal prosecution and civil claims for damages.

First published 1985

Published by

Higher and Further Education Division

MACMILLAN PUBLISHERS LTD

Houndmills, Basingstoke, Hampshire RG21 2XS

and London

Companies and representatives

throughout the world

Printed in Great Britain by Camelot Press Ltd, Southampton

British Library Cataloguing in Publication Data Bannister, B.R.

Interfacing the BBC Microcomputer.

(Macmillan microcomputer books)

1. Computer interfaces 2. BBC microcomputer I. Title

001.64'04 TK7887.5

ISBN 0-333-37157-7

# **Contents**

| Preface                                 | vii            |  |

|-----------------------------------------|----------------|--|

| 1 Input-Output Facilities               | 1              |  |

| 2 The User Port                         | 19<br>43<br>57 |  |

| 3 Analogue Signal Handling              |                |  |

| 4 The 1 MHz Bus                         |                |  |

| 5 Some Applications                     | 76             |  |

| Appendix A: Transistor-Transistor Logic | 102            |  |

| Appendix B: Machine Code Programming    | 107            |  |

| Appendix C: Input-Output Memory Map     | 111            |  |

| Appendix D: Data Sheets                 | 112            |  |

| Appendix E: Summary of Connections      | 148            |  |

| Index                                   | 151            |  |

## Preface

The BBC microcomputer is a very versatile machine in its own right: it has excellent facilities for problem solving, data handling, games, and graphics and sound generation. With the addition of a printer and a disc (or cassette) unit, and perhaps other standard peripheral devices, the computer forms the core of a powerful system. However, an extremely flexible system can be created by anyone who can make use of the wide-ranging input and output facilities provided by the manufacturer, to add their own circuits, or to interact with other systems.

Initially, having acquired the computer, or at least the use of it, a user will be concerned with driving the computer itself. However, having become conversant with BASIC, and possibly machine code programming, the more imaginative user will see many possible applications, most of which will require the addition of external devices. In the widest sense, these applications involve the elements of control: taking readings from some equipment, or sensing the settings of switches or relays; controlling indicator lights or the position of a stepper motor; and so on. By bringing the two operations of input and output together, we can then automatically detect certain conditions and, perhaps, sound a warning, or even adjust the input or output settings according to pre-determined rules.

This book explains how to set about building such systems. It explains the interfacing features that are available on the BBC micro and how to make the best use of them in a wide range of applications. Suitable devices are introduced and techniques for using them are explained, with practical examples chosen to illustrate the basic ideas. These can then be extended in many ways, limited only by the reader's imagination (and pocket!).

The book does not assume a high level of technical ability, although an understanding of transistor action is desirable. Certainly staff and students in schools and colleges will find the book most useful, and it should present no difficulties to the 'advanced' hobbyist.

Components used in the circuits described are all relatively cheap and are available from recognised distributors such as Farnell Electronic Components Ltd and RS Components Ltd. Program listings with comments are included throughout, but the comments should be omitted when copying the programs for use in the computer. The logic symbols used are ANSI Mil. Spec. symbols as used by Acorn Computers Ltd.

viii Preface

'Acorn' is a registered trademark of Acorn Computers Ltd. Throughout the book, the interpretation of published material is the authors' own and does not imply any endorsement by Acorn Computers Ltd.

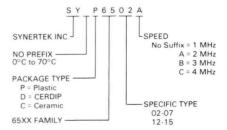

We gratefully acknowledge permission from NEC Electronics (UK) Ltd, Synertek Inc. and Texas Instruments Ltd to publish the data sheets contained in Appendix D. Finally we owe thanks to Don Whitehead for his helpful comments, and to Debbie Eaton for typing the manuscript.

The University, Hull 1984

B. R. BANNISTER M. D. WHITEHEAD

## 1 Input-Output Facilities

The BBC microcomputer has many advanced features that are not normally provided on computers of this size. Three general principles seem to have been foremost in the drawing up of the design specification:

To make programming of the computer as easy and flexible as possible by providing an enhanced BASIC and the ability to make use of multiple programs and assembler language sections.

To include many of the features found only in rudimentary form on other microcomputers, such as high-resolution colour graphics, complex sound generation, programmable keys, and so on.

To provide extensive interfacing capability, allowing the computer to form part of an extended system communicating with discs, printers, second processors, Teletext and even other computers via Econet, and able to accept new devices which may be produced as the technology develops.

It is the third area, of interfacing, with which we are concerned and we shall see that there are many ways in which the user can add extra circuitry for specific purposes, so taking full advantage of the flexibility that has been built in. This first chapter summarises the input and output facilities provided on the BBC model B microcomputer, but we first set the scene by considering some of the fundamental ideas that are necessary to the understanding of the transfer operations involved.

The average user scanning the circuit diagram of the microcomputer would see a bewildering array of symbols and interconnecting lines. A more practised eye, however, will recognise that there are distinct blocks of circuitry arranged to carry out specific tasks. In each block, one or two specialised large-scale integrated circuits are used, with additional logic gates providing what the designers call 'glue logic' to hold the system together. Between the blocks run the interconnecting wires arranged as two distinct buses, or highways, known as the data bus and the address bus, and a third, less well-defined, control bus made up of the controlling signals needed to ensure correct timing and the general smooth running of the system.

The heart of the computer is the microprocessor, which is where the program instructions are actually carried out, and which controls, and responds to, the other sections. The processor relies heavily on the memory sections which are of two types. One bank of chips makes up the read/write memory, which is general-purpose memory to hold user programs and data, and also to store the data needed

in continually refreshing the video display. Another bank of chips is the read only memory, ROM, containing the system programs that must always be available whenever the computer is switched on. The read/write memory is normally referred to as random access memory, RAM, since any location can be addressed and selected as readily as any other. But bear in mind that ROM is equally randomly accessible, unlike cassette or disc memory where data is stored in a serial form.

Any program, whether originally in machine code or in BASIC, or indeed in any other language, is ultimately processed by the computer as a succession of instructions which are executed consecutively. The processor runs a repetitive cycle in which the next instruction is fetched from memory and decoded, and then the indicated operation is carried out.

Each instruction must provide sufficient information for the processor to carry out the operation satisfactorily. The first section, or *field*, of the instruction is one byte long, and carries a code indicating the particular operation required. The list of available operations is called the *instruction set*, or *op-code set*, and each mnemonic of the assembler language corresponds to one of the op-codes. In some cases the instruction is complete in the one byte, but most instructions require additional information which normally gives the address of one of the operands to be used. Where this is the case, the code of the first byte also indicates that the fetch operation must be extended to retrieve the address field data, which can require one or two more bytes.

In executing the instruction, the address code defining the memory location of the operand to be used at a given time is generated by the processor and is distributed on the 16-bit unidirectional address bus. The data involved is carried on the 8-bit data bus, which has driver circuits that enable it to operate bidirectionally, and the drivers must be switched to the appropriate direction by the processor. Both the address bus and the data bus are extended to link all the other blocks of the computer circuitry.

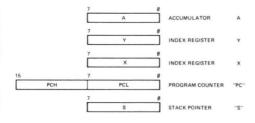

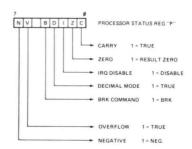

The majority of the time spent by the processor, as in any computer, is concerned with transferring data from one location to another. Data bits are moved around internally on the data bus, and each group of eight bits forms a byte which, in many cases, represents one character. The bytes are transferred between registers of various types, where a register can be thought of as a temporary store for the data bits but having a different name and characteristics dependent on the job that it is required to do. The first type, high-speed registers inside the processor, are used as working registers in carrying out the operations specified by the successive instructions of the program. The 6502 processor used in the BBC microcomputer has one *accumulator*, A, and two *index registers*, X and Y, directly available to the programmer, but also makes use of a 16-bit *program counter*, PC, an 8-bit *status register*, a *stack pointer*, and some auxiliary registers.

The second type is the random access memory, which is an array of registers designed to hold programs and data. Read only memory can also be considered as an array of registers that have been modified to retain data in a permanent, or

semi-permanent, form, so that we can easily read from any desired location, but can write in new data only with special equipment, if at all.

When we come to transferring data into or out of the computer we use a third type of register known as an *input port* or *output port*, and many of the specialised input-output (I/O) chips use other internal registers to provide appropriate control over how the ports operate at any given time.

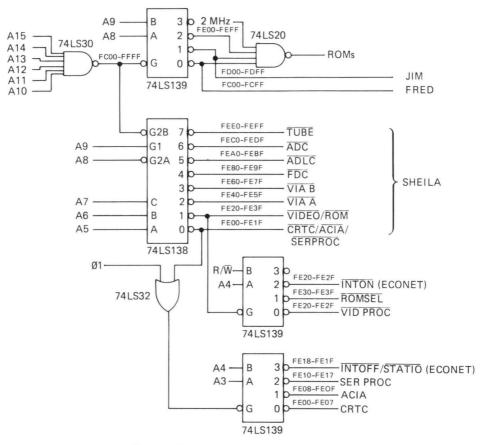

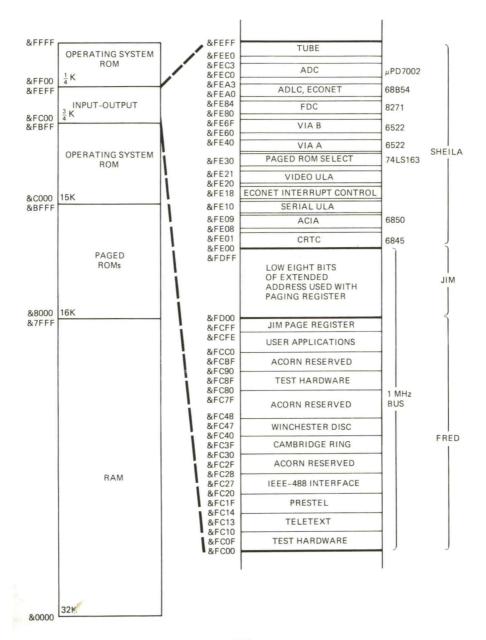

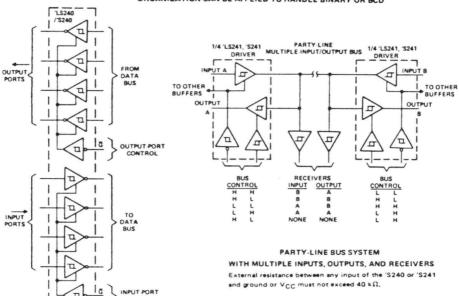

In all cases, however, an individual register is uniquely defined by its 16-bit address which is generated by the processor and distributed on the address bus. In fact, therefore, all transfers to and from input and output ports, and their associated control registers, are treated as memory transfers, and the system is said to use memory-mapped I/O. The User Guide provides a memory map that shows the allocation of all 65 536 (64K) locations from &0000 to &FFFF (the ampersand, &, is used to denote a hexadecimal number). The input-output area of the map is from &FC00 to &FEFF, and is considered as being made up of three sections of 256 bytes each. These sections are known, in Acorn literature, as FRED, from &FC00 to &FCFF, JIM, from &FD00 to &FDFF, and SHEILA, from &FE00 to &FEFF. SHEILA is the area devoted to internal input-output devices and, within that area, individual controller chips used in the microcomputer are selected by use of 74LS139 dual 2-line-to-4-line, and 74LS138 3-line-to-8-line data selectors, figure 1.1. When a data selector chip is enabled by the G input signals, one and only one of the outputs goes low.\* The 74LS138 data selector in figure 1.1, for example, is selected when input G1 is high and G2A and G2B are low. G2B is taken low when the inputs to the 74LS30 NAND gate are all high, or 1, so the 74LS138 is selected when address bit A8 is at 0 and bits A9 to A15 are at 1. This means that the data selector reacts only to addresses that begin with &FE, since &FE is a shorthand way of representing the binary value 11111110. The particular output of the selector that goes low is then determined by the values on the remaining three inputs, A, B and C, controlled by address bits A5, A6 and A7. This method of selection allocates a block of addresses for each device, but they may not all be required. The CRT controller chip, for example, has the eight locations &FE00 to &FE07 allocated, but only the first two are used.

The JIM and FRED areas are used in conjunction with the 1 MHz bus and will be dealt with when we come to consider the action of that bus.

The setting up of a port, and subsequent writing of data into or reading data from the port, is carried out under program control. Although the computer circuitry responds only to machine code, the program may be written in either assembler language or BASIC, which is then translated to the form required by the processor. In BASIC the statements are of the form

<sup>\*</sup> Logic values are indicated by voltages, and are said to be 'low', or logic 0, when the voltage is approximately zero, and 'high', or logic 1, when the voltage is something between about 3.5 and 5 volts. A small circle on the logic symbol indicates that output or input is active when low.

Figure 1.1 Address decoding circuitry

10 ?&FE62 = 255

meaning 'set location &FE62 to 255', or

10 A = ?&FE60

meaning 'set variable A to the value read from location &FE60'. The initial 10 is the line number in both cases. In assembler form the corresponding instructions would be

LDA #&FF STA &FE62

for the first, and

LDA &FE60

for the second.

Assembly language is faster than BASIC and much more compact, so it is often useful in dealing with data transfers through input-output ports which would otherwise interfere with the smooth running of the main program. An understanding of assembly language (that is, machine code) programming is very desirable, and sometimes allows access to features of the computer not otherwise available. A brief introduction to machine code programming is given in appendix B.

In all but very short sections of assembly language it is convenient to make use of the standard routines that have been provided in the operating system programs, using \*FX and OSBYTE calls. This is also good programming practice because it means that your programs are relocatable if and when you modify or extend your system. Full details of these calls are given in section 42 of the *User Guide*, but the method of operation is always the same.

The required routine is indicated by the number of the call, and a linking routine is necessary to point the processor to its first instruction. All the routines, including the linking routine, are held in ROM since they form part of the operating system. Being in ROM, however, means that we are unable to write the start address directly into the link routine and we must achieve the transfer indirectly. The linking routine is held in ROM, starting at &FFF4, and it makes use of a pair of bytes in RAM, located at &020A and &020B, and given the label BYTEV, which stands for Byte Vector. When an \*FX or OSBYTE call is made, the number of the call is placed in the accumulator, A, and the value is used to determine the start address of the routine. The start address is written into RAM as the Byte Vector, BYTEV, and the linking routine now merely needs to be an indirect jump to the routine using the vector provided. The actual sequence is

| Location                | Hex code       | Mnemonic    | Meaning                  |  |

|-------------------------|----------------|-------------|--------------------------|--|

| &FFF4<br>&FFF5<br>&FFF6 | 6C<br>0A<br>02 | JMP I BYTEV | Jump indirect to &020A/B |  |

Thus, when the \*FX or OSBYTE call finds the 'Jump to subroutine at &FFF4' instruction, it is told to do another jump to the start of the routine which begins at the address it will find in locations &020A and &020B, and so arrives at the correct starting point.

Any values needed by the call are first placed in the X and Y registers, and if there are any values to be returned by the call they also use the X and Y registers.

In dealing with data transfers to and from input-output devices mapped onto the memory area SHEILA, we could present our earlier examples in OSBYTE call form as

```

LDA #&97 /Prepare OSBYTE call to write to SHEILA

LDX #&62 /with offset &62

LDY #&FF /and &FF as the value to be written.

JSR &FFF4 /Call OSBYTE.

```

```

LDA #&96 /Prepare OSBYTE call to read from SHEILA LDX #&60 /with offset &60.

JSR &FFF4 /Call OSBYTE.

```

It is particularly easy with the BBC computer to insert assembler sections into BASIC programs, since the assembler is included in the BASIC interpreter. The DIM P% statement, for example, provides a simple way of reserving a block of memory for assembler code as it becomes necessary. When the BASIC program is run, the DIM statement is used to set aside a block of memory locations for the machine code section of the program, which is listed later. As we have seen, the microprocessor uses the program counter to indicate where its next instruction starts, but, until the program is run, the actual program counter value, P%, corresponding to the start of the section, is unknown. We therefore refer to it as a variable, such as PROG, which we define at the start of the machine code section. The length of the block of bytes reserved can be specified, and, where the exact number of bytes required is not known, it is sensible to include some value large enough to ensure some spare bytes. For example

#### 10 DIM PROG 29

reserves thirty bytes of memory for a machine code section starting at location PROG. The actual value of PROG is allocated by the interpreter when the program is run, and may change if the program is changed. Subsequently we set the program counter by means of a statement of the form

```

100 P% = PROG

```

P% can be set directly to an absolute value if required. We follow with the assembler code, which must be in square brackets, thus:

```

10

DIM PROG 29

Reserve 30 bytes at PROG

100 P% = PROG

/Set PC to allocated start value

120 [

Start of machine code section

130 .LIGHTS

Reference label

140 LDA #151

/Program code

150 LDX #&60

160 LDY &70

170 JSR &FFF4

180 RTS

/Return from subroutine

190 ]

/End of machine code section

200 etc.

/Continue with BASIC statements

280 CALL LIGHTS

/Call machine code section LIGHTS

```

Line 130 contains the reference label acting as the name of the machine code routine. It must be preceded by the full stop which causes the assembler to allocate the program counter value as a variable. This can be used in BASIC sections of the program as well as machine code sections. The routine is ter-

minated by the RTS, return from subroutine, instruction and the closing square bracket.

As part of its duties, the assembler must allocate specific locations to the labels defined by the program writer. The assembler scans the program twice: during the first scan, listing all labels, and during the second, matching the labels to the locations allocated. The labels are used when program jumps are called for, and during the initial stages of the assembly process any jump forward in the program will refer to a label that has not yet been defined in terms of a memory location. The assembler includes error-checking routines which, among other tasks, look for undefined labels, and, during the first pass, we must switch out the checking routines, though at all other times, of course, we wish to have them operating. This is normally achieved by use of the OPT directive to the assembler, in conjunction with a FOR statement. For example, we would add extra lines to our previous listing to give

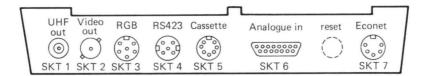

We are now ready to look at the input-output facilities that are provided on the computer, and to see how they can be used. If we go first to the back of the computer, we see a range of connectors, as shown in figure 1.2. Many of these give access to circuits that are designed for particular purposes, but others, such as the analogue and RS423 ports, are more general purpose.

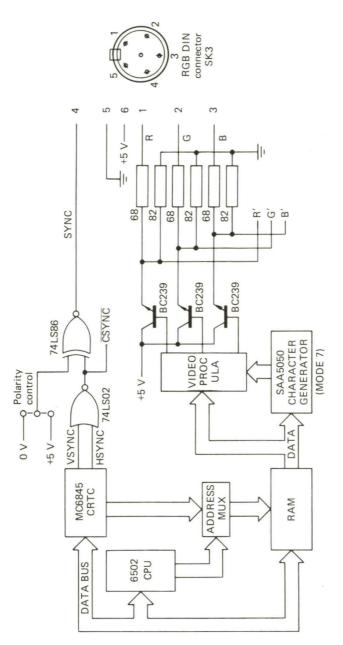

The three sockets at the left are all concerned with the connections of the display unit so we shall look first at the video signals provided. These allow the computer to display text or graphic information held in the video memory. Unlike many other microcomputers, this one uses a bit-mapped display and, except in mode 7, does not use a character generator ROM. This means that one bit of memory is provided for every addressable spot, or *pixel*, on the screen, so that the hardware can produce high-resolution displays with graphics and text intermixed. It does, however, necessitate a large video RAM area: in fact it needs up to 20 kbytes of RAM in the highest resolution modes, to cater for 81 920 pixels, giving 32 lines of 80 characters each on an eight by eight dot matrix (mode 1) or fewer pixels with more colours (modes 2 and 3). In the Teletext mode, mode 7, a maximum of only 1 kbyte of memory is required since standard character codes are stored and the character writing information is then provided by the SAA5050 character generator.

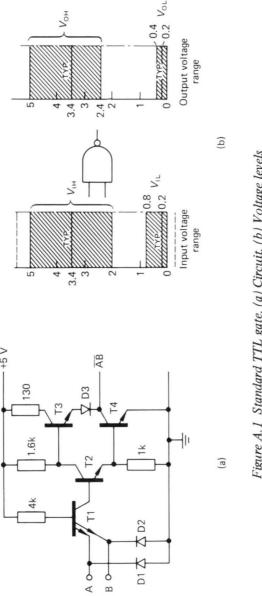

Figure 1.2 Connectors viewed from rear of microcomputer

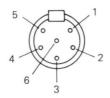

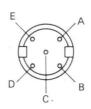

The video circuitry consists mainly of a Motorola MC6845 CRT controller, CRTC, working in conjunction with a custom-designed video-processor chip which produces the three video signals, red, green and blue (RGB) as correctly timed sequences for a high-quality colour monitor set. The three colour signals, together with a composite synchronising pulse signal, all at TTL levels (see appendix A), are brought out to the six-way DIN connector, SK3, labelled RGB, figure 1.3. A composite video signal for use with a PAL baseband monitor set is created from R', G' and B' by a simple summing amplifier (as shown on page 504 of the *User Manual*). This is brought out to the BNC socket, SK2, labelled 'video out'. Finally, another version of the composite video signal is used to modulate a UHF signal giving an output suitable for use with a conventional domestic PAL colour television receiver, operating nominally on channel 36. The UHF signal is brought out to the Belling-Lee coaxial socket, SK1, labelled 'UHF out'.

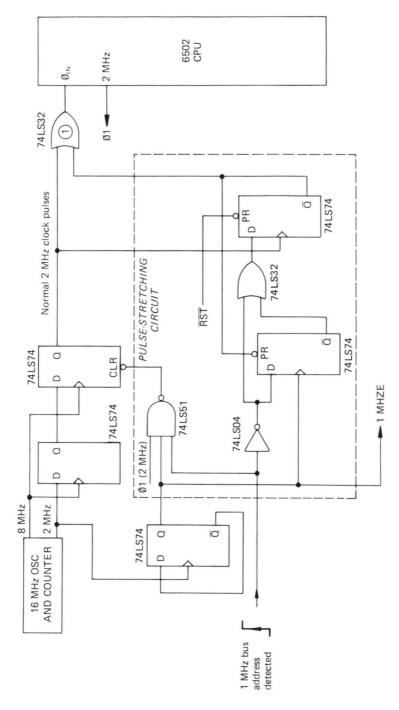

The video circuitry must also deal with the refreshing of the memory. The memory devices used are sixteen MB8118,  $16K \times 1$  bit dynamic RAMs giving a total memory of 32 kbytes. Dynamic RAM is used because it is very fast in operation, but it must be refreshed regularly so as not to lose the data held in it. This is done by the CRTC. As the CRTC and the 6502 processor cannot be allowed to access the memory simultaneously, they must alternate, or interleave, their demands. The 6502 processor is therefore clocked at 2 MHz (though we shall see that it can be switched to run at 1 MHz when required) so that it requires access to the memory every 500 nanoseconds. But the memory is fast enough to allow two accesses in that time and each 500 nanosecond period gives one access for the memory and one for the CRTC.

The next two sockets provide for serial data transfers either at standard RS423 levels or in a coded form suitable for use with a domestic cassette recorder. The RS423 serial data communications standard is an updated version of the well-known RS232-C or V24 standard which is used extensively by terminals and modems. Inexpensive networking controllers, such as Clearway,\* can also make use of the RS423 connection.

Data transfers on this serial port need only two lines for the data: one for incoming data, Receive Data, and the other for outgoing data, Transmit Data. A common return line is provided. In addition, two control lines are used:  $\overline{RTS}$  (Not ready to send) and  $\overline{CTS}$  (Not clear to send). The control signals are specified

<sup>\*</sup>Produced by Realtime Developments Ltd.

Figure 1.3 Generation of the video signals

in the negative sense because each normally sits at the higher voltage level and is taken low when the transmitter is ready to send or the receiver is ready to receive respectively. The receive and transmit directions are appropriate to the device only at one end of the connection, of course, since data in the transmit direction, for example, is received data to the device at the other end of the line. Care must therefore be taken in connecting devices to the serial port, and often a fair amount of trial and error is necessary before the connections are correct.

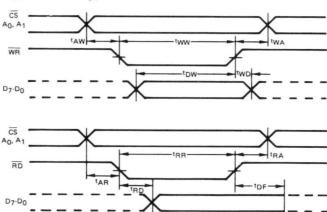

The conversion of an eight-bit data byte to serial form, and vice versa, is carried out by a Motorola MC6850 Asynchronous Communications Interface Adaptor, ACIA. This type of device is often referred to as a UART, standing for Universal Asynchronous Receiver/Transmitter. The ACIA arranges that the transmitted data is formatted correctly or *framed*, as in figure 1.4, with an initial START bit and a

Figure 1.4 Framing of an eight-bit data byte

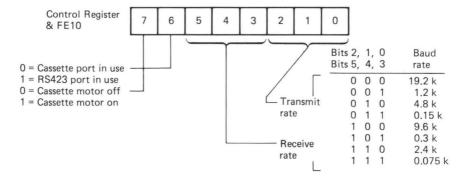

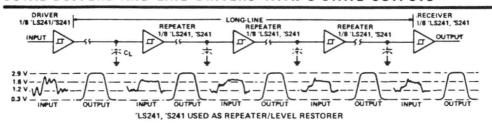

final STOP bit. Similarly with received data the ACIA checks for correct formatting before extracting the required data bits. The negative-going edge of the START bit indicates to the receiver that a character is on the line and, after confirming a genuine start, the receiver clock is arranged to sample the data at about the middle of the bit period as each bit arrives. The correct timing is ensured by the receive and transmit clock signals which are generated by another special custom-designed signal processor chip. This chip contains a control register which is selected by address &FE10, and allows the clock rates to be adjusted to one of eight values indicated in terms of the baud rate, figure 1.5. The baud rate can be considered as the number of bits per second on the serial line, and ranges from 75 to a slightly optimistic 19 200 bits per second. Transmit and receive can operate at different rates if required.

Figure 1.5 Allocation of bits in the serial processor control register

When the RS423 port is in use, the signals to and from the ACIA are passed directly through the serial processor chip and its associated buffers, and connections are made at the five-pin DIN socket, SK4, marked RS423. The cassette port can be brought into use by setting bit 6 of the register &FE10 to '1'. In this mode the ACIA is still used to convert parallel data to serial, and vice versa, but the serial processor chip now plays a much larger part.

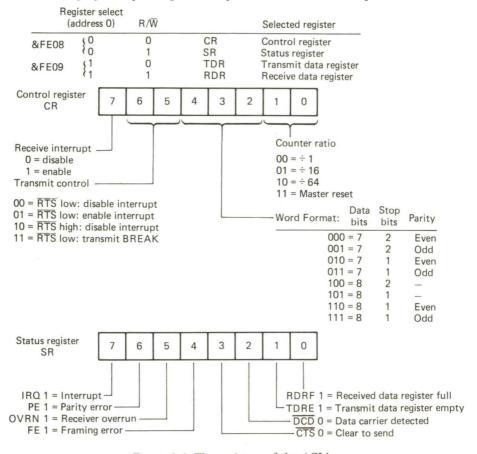

The mode of operation of the ACIA is determined by values in two registers, control and status, and two further registers carry the data in and out. Since a control register, which accepts commands, needs only to be written to, and a status register, which reports conditions, needs only to be read, the two registers share a single address, &FE08. Similarly the data registers share one address, &FE09, and writing transfers data to the transmit register, whereas reading takes data from the receive register. The detailed allocation of bits in the registers is summarised in figure 1.6, but for most purposes these are set-up and interrogated automatically by the operating routines provided in the microcomputer.

Figure 1.6 The registers of the ACIA

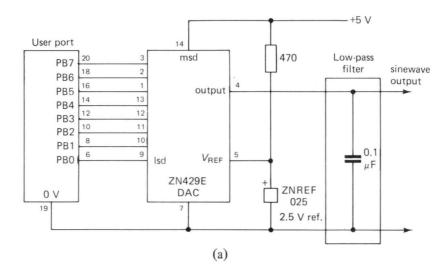

Continuing along the connectors we come next to the analogue inputs socket which is where we can, with suitable adjustments, connect any voltage that is not already coded digitally.

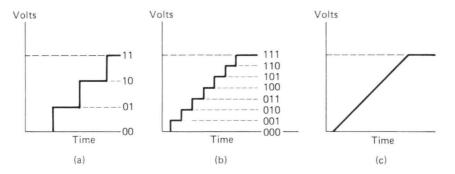

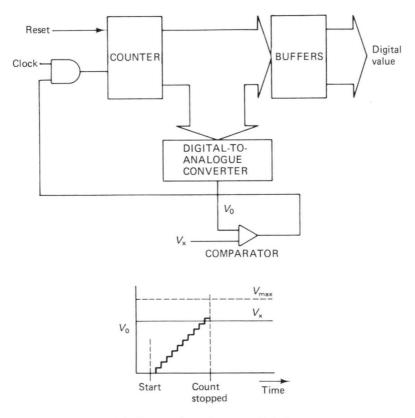

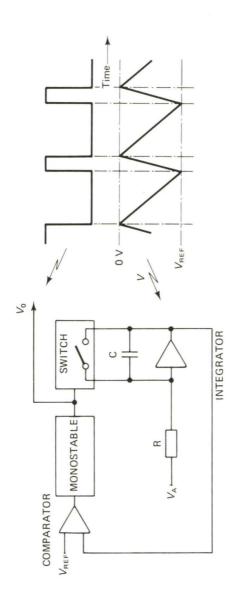

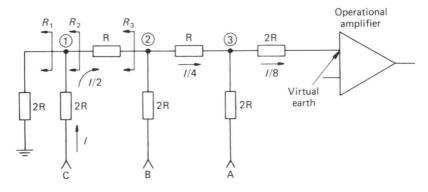

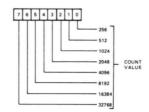

The computer operates in a digital framework, and the voltages it handles can exist only at certain levels which we designate '0' and '1', but we can cope with other voltages by means of special converter circuits. We can generate such voltages using a digital-to-analogue converter circuit, DAC, as we shall see later. The DAC gives an output voltage that is proportional to the digital value provided to it, and any change in the digital value causes a step in the resulting output voltage. We can easily set the voltage to any of the  $2^n$  levels available from n bits in the code: for example, eight bits would give us 256 possible levels, ten bits 1024 levels, twelve bits 4096 levels, and so on. If we allocate more bits to the code representing the voltage there are more possible levels, and the step between adjacent levels becomes smaller. If we could increase the number of bits in the code to an infinitely large number, the step between levels would become infinitely small, figure 1.7. We then arrive at an analogue representation of the voltage, since an

Figure 1.7 Step size decreases as number of bits in code increases

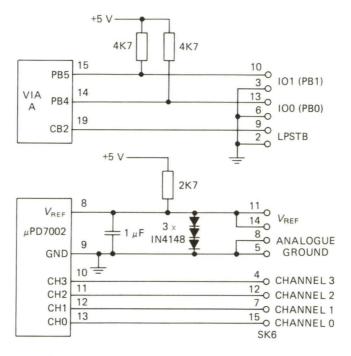

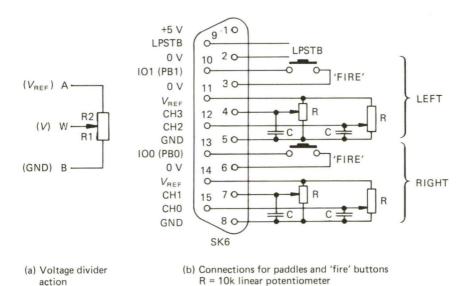

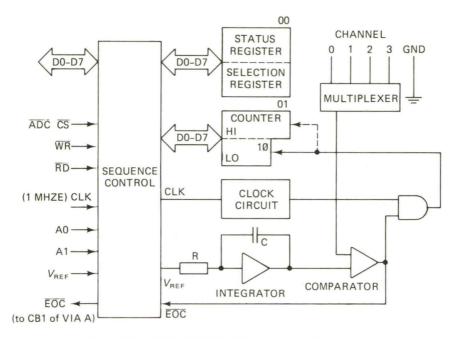

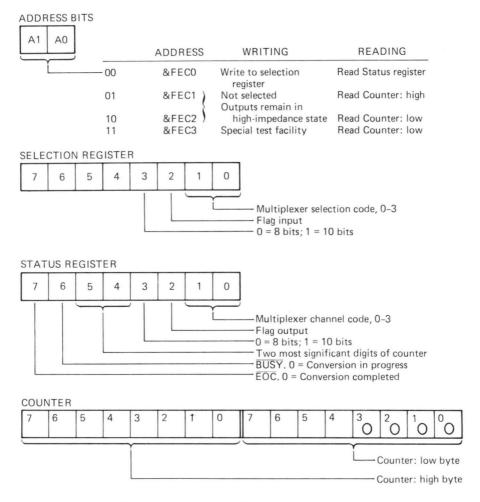

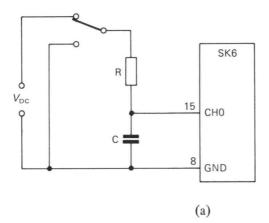

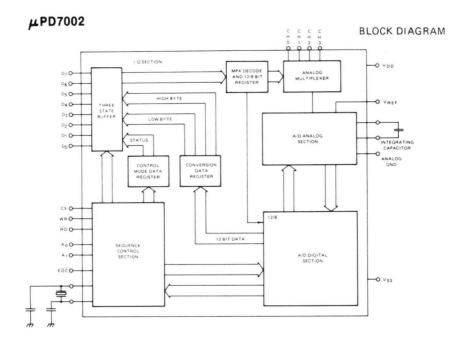

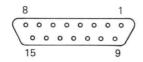

analogue voltage can take any value between the low and high limits. The voltages coming from transducers that measure variables in the 'real' world are almost invariably analogue in form. We therefore need a method of converting from the analogue to the digital form, and this is done for us by the  $\mu PD7002$  analogue-to-digital converter, ADC, provided in the computer. The  $\mu PD7002$  has four analogue inputs and these are brought out to the 15-way D-type socket, SK6, which is where the games paddles and light pen are normally connected, figure 1.8.

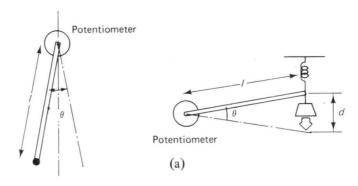

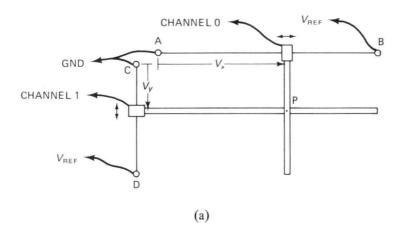

A games paddle is merely a variable resistor, or *potentiometer*, similar to those used as volume controls on radio and television sets. Two of the three terminals, A and B in figure 1.9a, are connected to the ends of the resistor, and the third is connected to the *wiper*, W. As the knob is turned, the ratio of R1 to R2 is varied, though (R1 + R2) remains constant as the total resistance between A and B. This value should be relatively small compared with the input impedance of the converter to which it is connected, typically greater than  $10 \, \text{M}\Omega$ , and yet not be so

Figure 1.8 SK6 connections for the analogue-to-digital converter

Figure 1.9 Potentiometer action and use in games paddles

C = 150 nF decoupling capacitor

small that it draws too large a current from the voltage reference circuitry. A value of about 10  $K\Omega$  is normally appropriate.

When the voltage  $V_{\rm REF}$  is applied across the resistor it acts as a voltage divider to give a voltage at the wiper of  $V = V_{\rm REF}$ . R1/(R1 + R2) so that V must always lie between 0 volts and  $+V_{\rm REF}$ . It is important that the maximum value of V is not too great for the ADC chip to handle and, although the  $\mu$ PD7002 converter is designed for a  $V_{\rm REF}$  of 2.5 volts, the computer designers have allowed a safety margin by providing a reference voltage of 1.8 volts. This should always be used if possible, as in figure 1.9b.

A joystick controller makes use of two variable resistors, so that, as the joystick is moved, the motion is resolved into two components at right angles and the resistors are adjusted accordingly. The four channels available on the  $\mu$ PD7002 means that it can handle up to two joysticks or four games paddles. The connector also carries the digital signals, which can be generated by the 'fire' buttons often provided on games paddles and joysticks. The 'fire' inputs are designated 100 and 101 and the signals are taken to bits 4 and 5 of VIA A which is the *Versatile Interface Adapter* used internally for a variety of tasks such as controlling the keyboard, sound and speech generators and so on. The state of the 'fire' buttons, '0' or '1', is written into memory from the VIA and is read by means of the X = ADVAL(0) command, to become the bottom two bits of the variable X, 100 affecting bit 1 and 101 bit 0. A command of the form X = ADVAL(0) AND 3 selects the bottom two bits to give X = 0, 1, 2 or 3 dependent on whether neither, left, right, or both buttons are pressed.

The final input, light pen strobe, LPSTB, is intended for use with a light pen which generates a pulse whenever it detects the passing of the electron beam that continually scans the display unit screen to refresh the information written there. The light pen contains an optical sensor which is illuminated by the phosphor glow as the beam of the cathode ray tube passes under the pen. The pulse it generates when illuminated is routed to input CB2 of VIA A and causes the normal sequence of operations to be interrupted, so that an operating system routine can be initiated to deal with it.

The operation of the  $\mu PD7002$  converter is considered in more detail in chapter 3. Early models of the computer included a RESET button next to the analogue inputs socket but this is not now provided though the wiring for it is still present on the board. A 'hard' reset is achieved on more recent models by pressing the CTRL and BREAK keys simultaneously.

The final connector on the back of the computer is used in interfacing the computer to the Econet. Econet is a local area network, LAN, developed by Acorn to allow up to 255 microcomputers to communicate and so share certain expensive facilities such as Winchester disc units, printers, and so on. The method of operation is very similar to Ethernet\* and uses a method known as carrier

<sup>\*</sup> A good description of Ethernet and other networking methods is given by K. C. E. Gee in *Introduction to Local Area Computer Networks*, Macmillan, 1983.

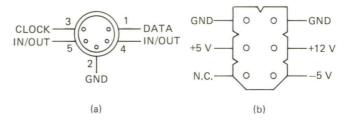

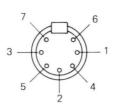

sensing multiple access with collision detection, CSMA-CD. All computers linked to Econet have equal status and are independent except that a common timing clock signal is taken from a designated one of the computers. A failure in one computer will not affect the operation of the network and adding more computers does not affect the inherent speed of data transfers. Inter-computer transfer rates, however, are dependent on the distance between the computers; for short distances, up to about a quarter of a mile, transfer rates up to 210 kbits per second are possible, but at a mile the maximum rate is about 100 kbits per second. Inter-connections are by 4-wire cable which gives a relatively low-cost network. The interface makes use of a Motorola 6854 Advanced Data Link Control, ADLC, chip with line driving and receiving circuits working in differential mode, through socket SK7, to provide data and clock lines, figure 1.10a. Each computer linked to the net is allocated a unique 8-bit station identity code which is set up on jumpers, designated S11, inside the computer.

Figure 1.10 (a) Econet connector. (b) Power extension socket

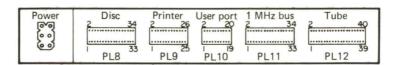

If we now look under the computer, by lifting up the front edge of the keyboard, we find many more connectors, figure 1.11. Apart from the power extension socket on the far left, these all come directly from the front edge of the main printed circuit board inside the computer and make use of *insulation displacement connectors*, IDC, ranging in size from 20-way to 40-way.

Figure 1.11 Connectors viewed from front of computer

Let us again take each connector in turn, starting, as before, with the leftmost one which, as we have noted, is the power extension socket. It is, in fact, a 6-way connector carrying +5 volts, -5 volts, +12 volts and ground returns, figure 1.10b, for use with a floppy disc unit when fitted. These supplies are not highly rated and are not intended to power other peripheral units, which should have their own supplies. However it is possible to draw a limited current at +5 volts for external use if the disc unit is not fitted.

The first of the IDC connectors is a 34-way plug, PL8, for use in interfacing to a disc unit operating to SA400 standard specification. The main bulk of the interfacing work is done by an Intel 8271 floppy disc controller, FDC, chip, which handles both the data transfers and the control signals. It can support two devices, referred to as 0 and 1, which can be either single-sided or double-sided and which use 8-inch,  $5\frac{1}{4}$  or the newer 3 or  $3\frac{1}{2}$ -inch diameter discs. The data rate can be switched between 125 and 250 kbits per second, as appropriate to the type of drive in use, by means of jumpers on the board. The signals involved in the control of a disc interface are complex and specialised, so it is not possible to make other use of them and we need discuss them no further here. The remaining connectors, however, provide interfaces which are more flexible to a greater or lesser extent.

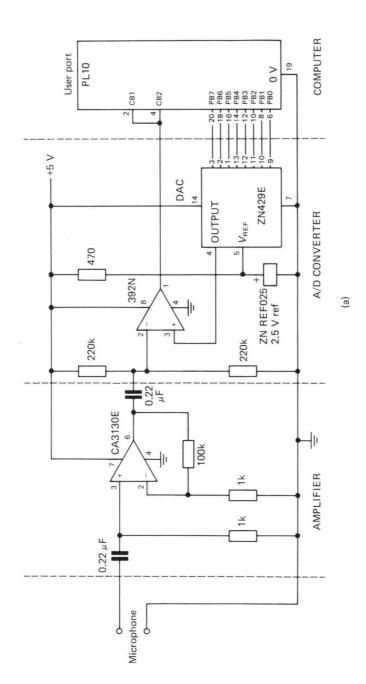

The next two connectors can be taken together as they make use of a single 6522 Versatile Interface Adapter, VIA, chip. The 26-way connector, PL9, is the printer plug which is connected to one-half of the VIA and, with its additional buffer circuits, provides a standard Centronics parallel printer interface. The software routines necessary to drive the interface are provided in the machine operating system. The other half of the VIA is connected to the 20-way plug, PL10, and provides the User Input/Output Port which has eight data lines and two additional control lines for general interfacing requirements. This is the most flexible port for the attachment of external circuits or equipment to the computer and a detailed review of its operation is given in the next chapter.

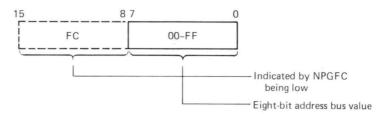

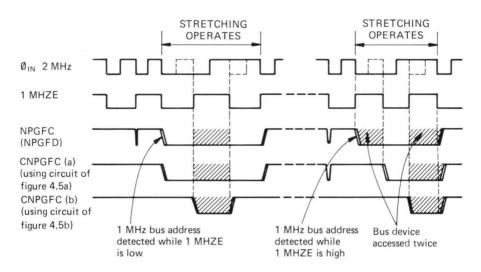

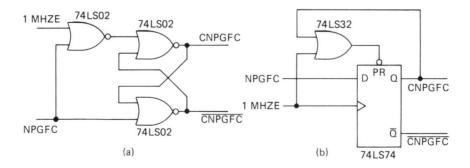

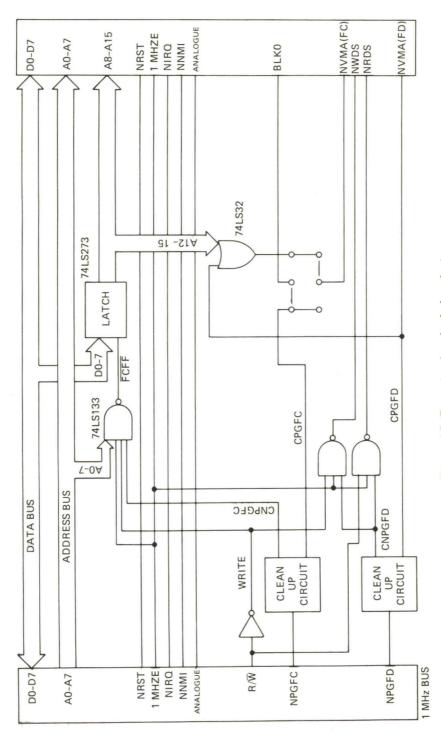

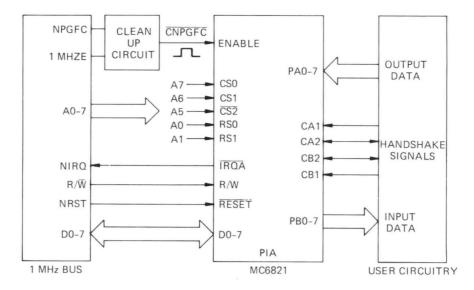

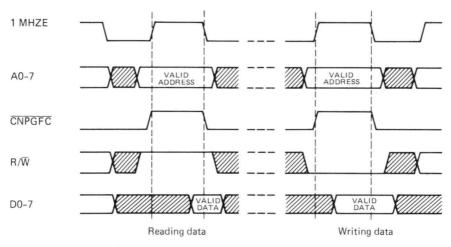

Moving to the next connector, we come to another general-purpose interface but one which is more structured for specific interfacing purposes when extending our computer system. The 34-way connector, PL11, carries what the designers have called the 1 MHz bus. It is so called because one of its main features is a 1 MHz clocking signal. The computer processor runs normally at 2 MHz but this is too fast for many of the standard components used in interfacing and the processor must be slowed down whenever a transfer on the 1 MHz bus is involved. The 1 MHz clock used externally, 1MHZE, is itself derived from the 2 MHz clock used internally by the processor and, when an address lying in the areas of FRED or JIM is detected (that is, an address starting with &FC or &FD), the 2 MHz clock is stretched to make one cycle last as long as one cycle of the 1 MHz clock.

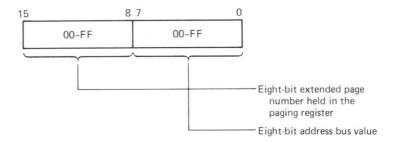

The 1 MHz bus carries the following signals: eight data lines, D0 to D7; eight address lines, A0 to A7; NPGFC; NPGFD; NRST; NIRQ; NNMI; 1MHZE; R/NW; ANALOG IN, and several ground return lines. Some of these need a bit of explanation. A full address in the computer needs sixteen bits and it is often convenient to think of it as made up of two parts: the upper half defining a page address with each page containing 256 bytes, and the lower half defining a particular byte within the page. In this representation, memory area FRED, which contains only addresses beginning with &FC, is then page FC, and similarly JIM is page FD. Because the decoded signals are low active, that is, they switch to logical '0' when selected, the bus signals are coded NPGFC and NPGFD, meaning 'not page FC' and 'not page FD' respectively. The bidirectional data bus drive circuits are arranged to be active only when NPGFC or NPGFD is present, and then only the

low eight address lines, A0 to A7, are required to define an address within the page. The direction in which the data bus drivers operate is controlled by the R/NW, read/not write, line with data transferred to the computer when the line is at '1', and from the computer when it is at '0'.

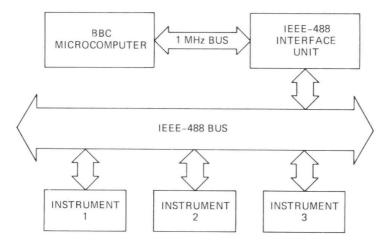

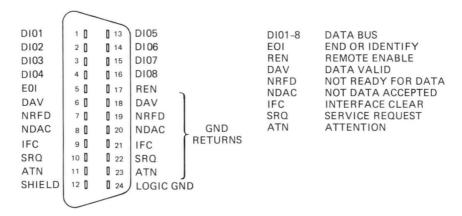

Page &FC, FRED, is intended for use with peripheral units requiring only limited memory space, and specific blocks have been reserved for Teletext, Prestel, IEEE-488 bus, Cambridge Ring, Winchester disc memory and test hardware. Other blocks are reserved for future use by Acorn, but one block of 63 bytes running from &FCC0 to &FCFE is allocated for general use, and it is best to restrict our usage to that area.

Page &FD, JIM, on the other hand, is intended for peripheral equipment requiring a larger memory space, and it makes available a total of up to 64 kbytes by use of an external paging register. The eight address lines, A0 to A7, available on the bus are used to define the location within a page; the eight-bit extended page number, which acts as the top eight bits of the address for the peripheral unit, is transferred on the data bus to the page register, which must be provided by the user and is itself addressed as location &FF on page &FC. A copy of the page register content is kept for internal reference at &EE of the zero page of the computer. The backplane card of the BBC Expansion Box, which is specifically designed for use with the 1 MHz bus, contains a page register with address recognition and signal shaping circuits, and its use is recommended wherever possible. The page register is reset to 00 by use of the NRST reset line provided on the bus. Again, a lot of the address space on page &FD is reserved by the manufacturers for specific uses. In fact all pages from &00 to &7F are reserved, which means that only the half of the pages that have a '1' as the most significant bit of the address are available to the user; that is, pages &80 to &FF.

All the signals described so far, except the reset, NRST, are high-speed signals which, when transmitted on an extended length of wire can give rise to reflections and crosstalk. It is therefore recommended that each line should not exceed about 2 feet (60 cm) in length, and should be correctly terminated by 2K2 resistors to +5 volts and ground. The load on each line should not exceed one LSTTL load. The three signals NRST, NNMI and NIRQ, however, are different and do not require termination; NNMI and NIRQ use open-collector gates (see appendix A) connected to give a wired-OR function, and the necessary pull-up resistors are provided as 3K3 resistors internally at the microprocessor. *Non-maskable interrupt*, NMI, and *Interrupt request*, IRQ, are signals that can be used to interrupt the program in the computer when external equipment requires attention. The wired-OR arrangement means that several devices can be attached to the line and any one is able to switch the line to the '0' active state. Interrupts are covered in chapter 2, when we look at the interface adaptors used in inputting and outputting.

One other feature of the 1 MHz bus is the ANALOG IN connection which provides a convenient way of coupling an external analogue signal to the internal audio circuits. The signal, which should not exceed 3 volts rms, is mixed with the output

of the sound and speech generators just before the audio amplifier which drives the loudspeaker.

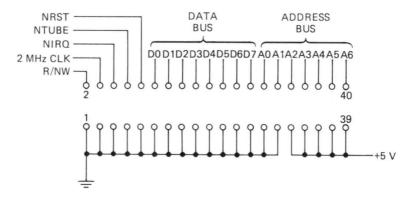

The final 40-way IDC plug is that for the *tube*, PL12. The tube consists of a few control signals and a set of connections directly onto the internal address and data buses of the computer, and as such should be used very carefully. In fact, as has been emphasised earlier, it is advisable to use the tube only in the way intended so that the operation of an extended system is not impaired. It is designed to allow very high-speed communication between the internal 6502 and a high-speed *second processor*, so that the BBC computer effectively acts as a slave, dealing with routine and time-consuming operations such as scanning the keyboard, refreshing the display and dealing with other input-output operations including transfers to disc, printer and so on. Several second processors are available or planned, ranging from the 6502 running at 3 MHz clock rate and with 64 kbytes of RAM, through the Z80 running at 4 MHz, again with 64 kbytes of RAM, enabling all CP/M based programs to be run, to the powerful 16032 16-bit processor, allowing up to 16 Mbytes addressing and with 32-bit internal data operations. The connections of PL12 are shown in figure 1.12 and we see that, although all eight data bits are

Figure 1.12 Connections to tube, PL12

brought out, only the seven lowest address lines are made available. The NTUBE select line goes low (that is, to '0') when a tube address is detected, and that occurs for any address from &FEE0 to &FEFF. These 32 locations are used in conjunction with the 7 address lines by a special tube controller chip to transfer data through the tube at the full 2 MHz clock rate.

## 2 The User Port

In connecting external equipment to a computer, one of the most common requirements is to light lamps to indicate the condition, or *status*, of the system, and to sense the settings of switches which are used to control the equipment. The user port is designed specifically for this sort of use and is, therefore, the first of the general-purpose interfacing provisions for us to look at in some detail. We recall from chapter 1 that it makes use of part of a Versatile Interface Adaptor, VIA, which provides a wide range of facilities to interface external circuits to the computer, and in order to control the flow of signals through the ports we must have a good understanding of how the device operates.

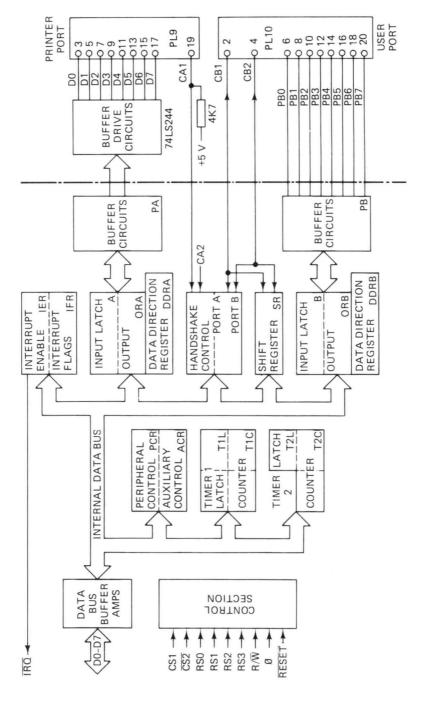

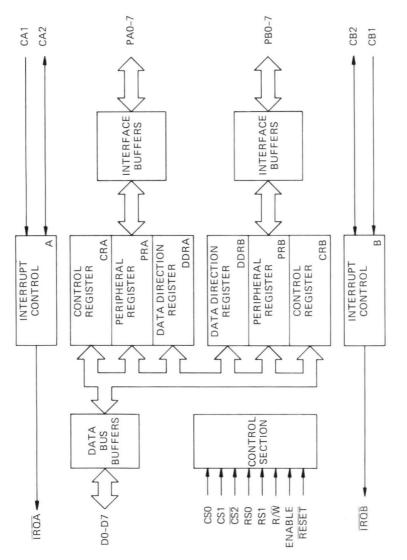

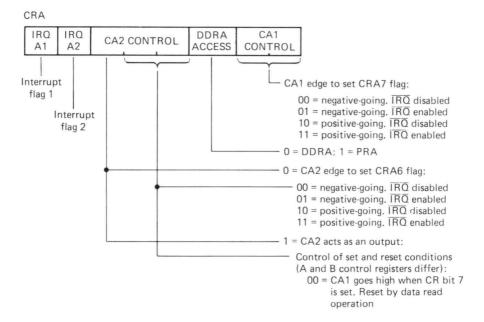

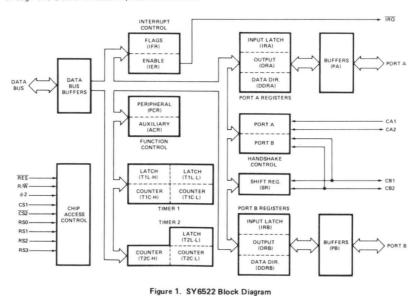

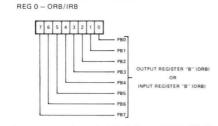

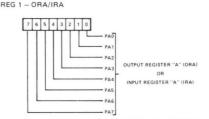

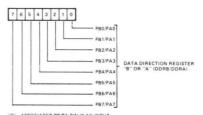

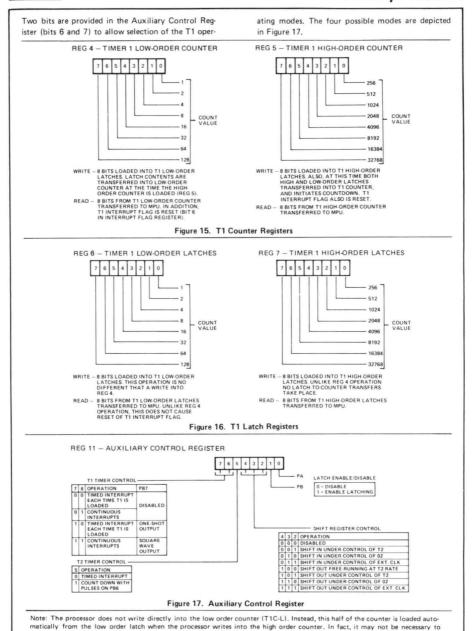

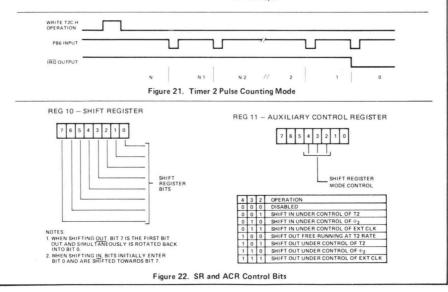

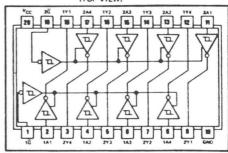

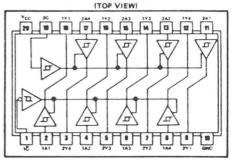

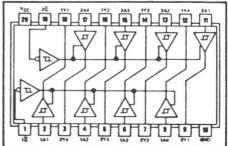

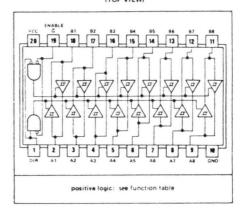

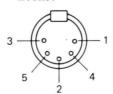

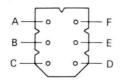

The main function of the VIA is the provision of two registers, port A and port B, each of which allows eight bits of data to be transferred to or from the computer in any desired pattern, but it also provides a shift register for parallelserial operation, and two internal timers. The way in which the ports, shift register and timers operate is controlled by the values held in additional registers inside the chip. These control registers are cleared to a quiescent, disabled condition when the internal reset line of the computer is taken to ground, as it is when poweringup the computer and when CONTROL/BREAK is generated. The appropriate bit patterns must therefore be loaded into the control registers during the initialisation program sequence which immediately follows the reset. Once the VIA is programmed to operate in a certain way, it will continue to do so until the bit patterns are changed. There are several different sections of the VIA, figure 2.1, with signals to and from the microprocessor on the left, and signals for external connections on the right. When we add up all the necessary registers inside the VIA we find that there are sixteen, so four inputs, RS0 to RS3, are provided to allow us to specify any one of them, and these inputs are controlled by address bits A0 to A3. In order to select, or activate, the VIA, the chip select input, CS1, must be at '1' and CS2 must be at '0'. CS1 is held permanently at '1' so selection is controlled by the VIAB signal which is connected to CS2 and is generated by the address decoding circuitry when the address range &FE60 to &FE7F is detected.

Address bits A0 to A3 indicate the individual register address and the full list of address codes is given in the table of figure 2.2. The remaining signals to the control section are used in carrying through transfers of data between the VIA and the 6502 microprocessor. These are under the control of the processor which uses the read-not write line,  $R/\overline{W}$ , to indicate whether it is providing data (in which case the  $R/\overline{W}$  line is at '0' indicating writing) or is expecting to receive data

Figure 2.1 Versatile Interface Adapter schematic

|    | RS3 | RS2 | RS1 | RS0 | ADDRESS |      | REGISTER                           |

|----|-----|-----|-----|-----|---------|------|------------------------------------|

| 0  | 0   | 0   | 0   | 0   | &FE60   | DRB  | Data register B                    |

| 1  | 0   | 0   | 0   | 1   | &FE61   | DRA  | Data register A                    |

| 2  | 0   | 0   | 1   | 0   | &FE62   | DDRB | Data direction register B          |

| 3  | 0   | 0   | 1   | 1   | &FE63   | DDRA | Data direction register A          |

| 4  | 0   | 1   | 0   | 0   | &FE64   | T1CL | Timer 1: write latch, read counter |

| 5  | 0   | 1   | 0   | 1   | &FE65   | T1CH | initiate count                     |

| 6  | 0   | 1   | 1   | 0   | &FE66   | T1LL | load latch, low byte               |

| 7  | 0   | 1   | 1   | 1   | &FE67   | T1LH | high byte                          |

| 8  | 1   | 0   | 0   | 0   | &FE68   | T2CL | Timer 2: write latch, read counter |

| 9  | 1   | 0   | 0   | 1   | &FE69   | T2CH | initiate count                     |

| 10 | 1   | 0   | 1   | 0   | &FE6A   | SR   | Shift register                     |

| 11 | 1   | 0   | 1   | 1   | &FE6B   | ACR  | Auxiliary control register         |

| 12 | 1   | 1   | 0   | 0   | &FE6C   | PCR  | Peripheral control register        |

| 13 | 1   | 1   | 0   | 1   | &FE6D   | IFR  | Interrupt flag register            |

| 14 | 1   | 1   | 1   | 0   | &FE6E   | IER  | Interrupt enable register          |

| 15 | 1   | 1   | 1   | 1   | &FE6F   | DRA  | Data register A, without handshake |

Figure 2.2 VIA register address codes

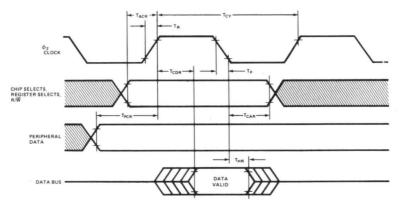

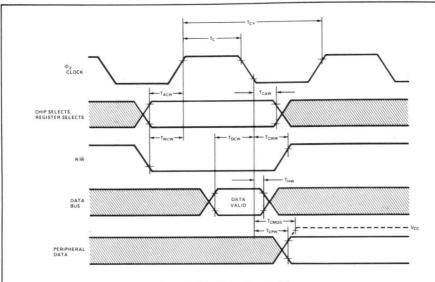

(in which case the  $R/\overline{W}$  line is at '1' indicating reading). The 1 MHz system clock,  $\emptyset$ , ensures the correct timing of the transfers.

The data registers in both peripheral ports, A and B, consist of eight data lines which can be programmed to act as inputs or outputs in any order, as defined by the settings in the corresponding bits of the associated *Data Direction Registers*, DDRA and DDRB. Setting a particular bit of a DDR to '0' ensures that the corresponding bit of the data register acts as an input, whereas a '1' ensures that the bit acts as an output. When a bit of the data register is programmed to operate as an output, the actual value of that bit is determined by the setting of the corresponding bit in the *Output Register*, OR. From figure 2.2 we see that DDRB is addressed as &FE62, so, to set up all eight bits of port B to act as outputs for example, we would load the DDR with 255. That is

10 ?&FE62 = 255

Thereafter, we output to port B merely by writing to the output register at &FE60. For example

40 ? & FE60 = A

The output register has no effect on bits of the data register that are programmed to act as inputs.

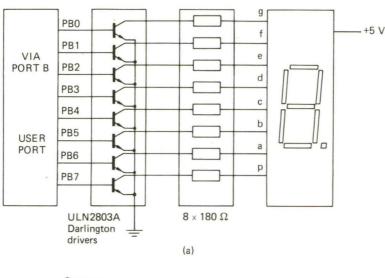

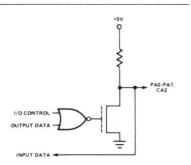

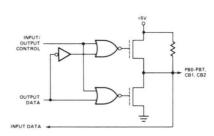

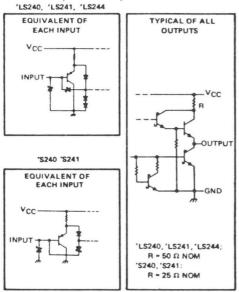

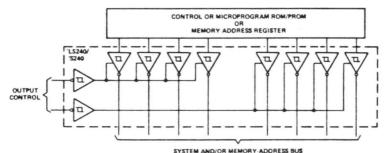

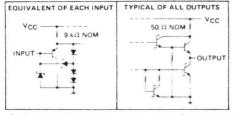

In addition to controlling the logical values on the lines of the data registers, we must also ensure that each output circuit is capable of providing the current necessary to drive whatever equipment we wish to connect. The drive capabilities of the two ports of the VIA are slightly different and anyway port A has been provided with additional buffer drive circuits since it is intended to act as the output port to a parallel printer, via plug PL9. The drive circuits are provided by a 74LS244 octal buffer-driver chip in which each output can drive up to 15 standard TTL loads (see appendix A for details of TTL operation). Because of these output

buffers, we cannot use port A as an input port but we can, of course, use it to drive equipment other than a printer if we wish, provided that we do not exceed the drive capabilities of the 74LS244 chip. Port B is connected to the output connector, PL10, directly, and each line will drive one standard TTL load. In addition, each line can provide a source current of one milliamp at 1.5 volts, allowing it to drive Darlington transistor circuits if required. A Darlington transistor, or more strictly a Darlington pair, is a compound connection of two transistors in which the collectors are connected together and the emitter current of the first transistor provides the base current of the second. The resulting current gain is the product of the two individual gains, so we get a high gain without increasing the overall base current demands, though the base-emitter voltage increases to about 1.4 volts.

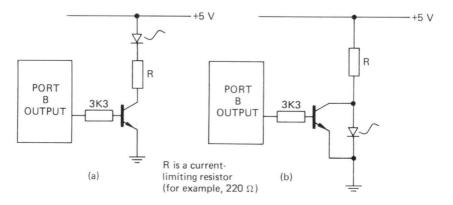

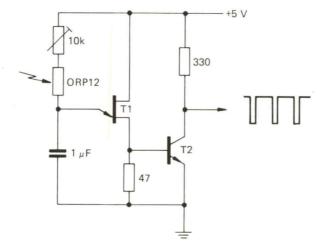

In many cases an output port is used to drive a set of indicators and one of the most popular types of indicator is the light emitting diode, LED, because it will operate at voltage and current levels similar to those directly available from the logic circuitry. A typical LED will give a good illumination when passing a current of 15 to 20 milliamps. Our output port circuits, however, will sink up to 1.6 milliamps when at '0', and will source a minimum of 1 milliamp when at '1'. Neither of these levels is sufficient to drive the LED directly, but we can employ a simple transistor amplifier to boost the current level. In the circuit of figure 2.3a, the transistor turns on when the port output is at '1', turning the LED on at a current level limited to a safe value by the series resistor. If it is required that the LED switch off when the port output is at '1', the circuit of figure 2.3b can be used.

Figure 2.3 Use of transistor to drive the LED. (a) LED ON when output at '1'. (b) LED OFF when output at '1'

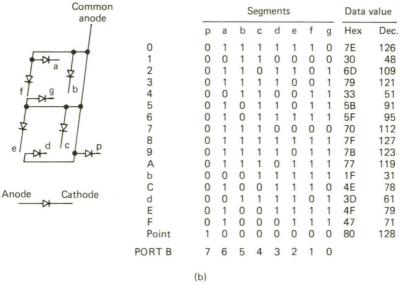

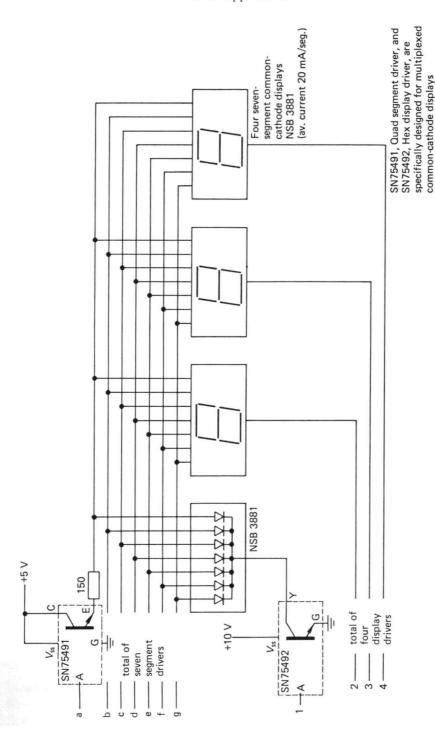

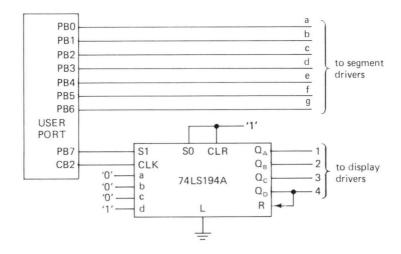

A seven-segment LED display is a single-digit numeric display, which is made up of seven light emitting diodes, and in many cases an eighth diode for the decimal point. In general, all the diode anodes are connected together, although common cathode versions are also available. We can thus drive one seven-segment display from our eight-bit user port, figure 2.4a. The individual decimal digits are

Figure 2.4 Driving a seven-segment LED display. (a) Segment connections. (b) Segment coding

formed by lighting the correct segments, and we can extend the idea to generate the full hexadecimal character set on the same display by including the six letters A to F, as long as we tolerate lower case b and d, so as not to confuse B with 8 and D with 0.

A program to output data to a single display is very simple. This one, figure 2.5, counts in decimal. Lines 60 and 70 use the internal timer, which counts in one-hundredths of a second, to define the half-second period during which each digit is displayed.

```

/Setup User Port as output

10 ?&FE62=255

20 I=O

/Initialize integer count

/Read bit pattern code

30 READ A

40 ?&FE60=A

/Output pattern to User Port

50 I=I+1: IF I>9 THEN I=0: RESTORE /Restart count

60 TIME=0

70 REPEAT UNTIL TIME > 50

/Pause

/Repeat

80 GOTO 30

90 DATA 126, 48, 109, 121, 51, 91, 95, 112, 127, 123

/This program counts repetitively

from 0 to 9.

```

Figure 2.5 Counting in decimal

A simple extension of the program, figure 2.6, allows us to display the value c any of the numeric keys on the keyboard. By pressing any key from 0 to 9 the value is displayed, and pressing the full stop illuminates the point. The point is permanently displayed until the full stop is pressed again. Further extension of the program, figure 2.7, will give us a flashing display. We choose here to flash at a visible rate, but in many cases a light emitting diode will operate more efficient if pulsed, and if pulsed sufficiently rapidly it still appears to be permanently on. The pulsing means that we can operate the LED at much higher current levels for short periods so that the average power dissipation is still not excessive. Many

```

10 ?&FE62=255

/Setup User Port

20 DP=0

/Ensure point is off

30 RESTORE

40 A=GET

/Input a value

50 IF A=46 THEN DP=128-DP

/If fullstop, invert msd

60 A=A-47

/Select data entry to match

70 IF A(1 OR A)10 THEN GOTO 30

/Key not numeric

80 FOR I=1 TO A: READ B: NEXT I /Read up to required code

90 C=B+DP

/Add point setting

100 ?&FE60=C

/Output to User Port

110 GOTO 30

120 DATA 126, 48, 109, 121, 51, 91, 95, 112, 127, 123

/This program displays the value of

```

Figure 2.6 Display numeric keys

any numeric key pressed.

to its other condition.

fullstop switches the decimal point

Pressing

systems use a higher drive voltage of 10 to 15 volts, with the LED pulsed on for a few milliseconds then off for a few milliseconds. We shall see later that this allows us to *multiplex*, or timeshare, the display so that we can deal with a large number of displays from a given number of ports.

```

10 ?&FE62=255 _____

/Setup User Port

20 RESTORE

30 A=GET

/Input from keyboard

40 IF A=70 THEN PROCflash

/Press F to flash

50 A=A-47

/Select data entry

60 IF A(1 OR A)10 THEN GOTO 20

/Key not numeric

70 FOR I=1 TO A: READ B: NEXT

/Read up to required code

80 ?&FE60=B

/Output to port

90 GOTO 20

100 DEF PROCflash

/FLASH procedure

110

?&FE60=0

/Clear output port

120

RESTORE

130

REPEAT

140

?&FE60=B

/Output bit pattern

150

TIME=0: REPEAT UNTIL TIME >50

/Pause

160

?&FE60=0

/Clear port

TIME=0: REPEAT UNTIL TIME >40

170

/Pause

180

A=INKEY(10)

/Press any key to stop

190

UNTIL A()-1

200

RESTORE

210

ENDPROC

220 DATA 126, 48, 109, 121, 51, 91, 95, 112, 127, 123

```

/A procedure "FLASH" is defined to switch display on and off for periods specified in lines 150 and 170.

Figure 2.7 A flashing display

In some cases we may need to control larger and more powerful lamps or other loads that cannot be driven directly from the interfacing circuitry, and it is then worth considering the use of relays, or power transistors or thyristors. All these devices are merely electrically controlled switches and there are many different types in many different shapes and forms. The important point to remember in every case is that the contact rating or current rating of the selected device must be high enough to cope with the expected load current.

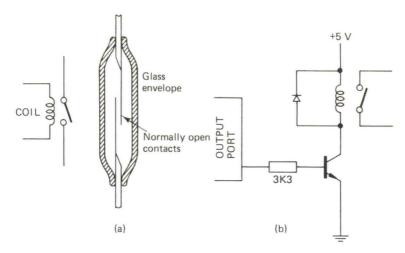

The simplest form of relay is the reed relay, figure 2.8a, which has usually a single normally-open contact that closes when the external coil is energised. In many cases the coil is designed to be driven directly from logic circuitry, and contact ratings up to about 0.5 amps are available. Larger, multiple contact relays are available but require driver transistors to energise the coils, figure 2.8b. As with all inductive loads, when switching the current in the relay coil, large transient voltages can be produced by the stored energy, and it is essential to connect a suitable diode across the coil in such a way that the transient voltage

Figure 2.8 (a) Reed relay. (b) Driving a larger relay

forward-biases the diode and is short-circuited. Many relays have the protective diode built in.

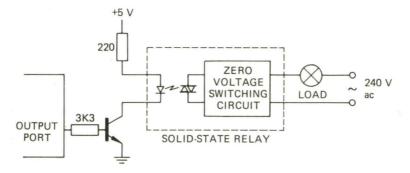

A very convenient type of relay for larger loads is the solid-state relay, SSR, which consists of a driver circuit optically coupled to a light emitting diode controlled by the input signal. The optical coupling ensures complete isolation between input and output circuits of the relay up to a voltage of several thousand volts. Since the input circuit of the relay consists of a diode, it can be driven very easily from the output port, figure 2.9. Low power rated opto-isolated drivers may have to use a second higher-rated relay to cope with heavy loads, but the larger solidstate relays can handle several amps and make use of a triac as the output driver. They often include zero-crossing detectors to control the switching point so as to prevent spikes being generated on the supply. The efficiency is limited, so these devices run quite warm and should be mounted on a suitable heat-sink. Another point to watch is that a logic '1' at the input of the SSR switches the relay on. When a VIA is initialised then each bit of the port is set as an input, which appears to the SSR as a '1', so if it is important to ensure that any equipment does not switch on until required, and can be switched off quickly by pressing the BREAK key, it is safest to control the SSR with a logic '0'. This can be achieved by putting an inverter, or simple common-emitter transistor circuit between the port and the SSR.

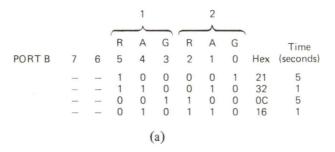

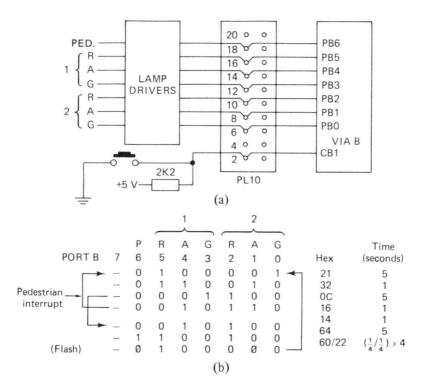

A common extension to the controlling of switches is the requirement to sequence the operations correctly so as to indicate necessary steps or to carry out an automatic routine. This can take a multitude of forms, but probably the best-known sequence is that used for traffic lights, and it forms a convenient illustration of the method fundamental to all control sequences. Programs of any desired complexity can be built-up around the basic sequence, to include with the

Figure 2.9 Use of a solid-state relay

traffic lights, for example, filter lights, biasing, pedestrian phases and so on. For our simple example we assume two sets of lights, which must sequence as shown in figure 2.10a, and a program to achieve this simple sequence, as given in figure 2.10b. Here we make use of a procedure, CHANGE, which itself makes use of a subroutine, LIGHTS. The subroutine involves an OSBYTE call to the SHEILA base address plus &60, that is, to the user port address, and the value to be sent to that address is placed in location &70. The procedure outputs the new pattern to the lights and then waits N seconds before sending out the next pattern. Merely by adjusting the output codes and time delays appropriately, this program can be used as the basis for a large range of sequencing controllers.

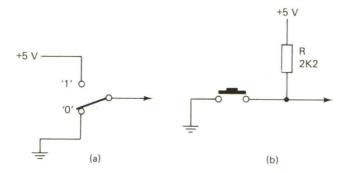

We have concentrated so far on outputting signals from the computer, but accepting signals is equally important, and that is what we now move on to. At this stage we will consider only those signals that are already in a digital form; that is, those that come from switches of some sort, so that they are either on or off. Simple switches and relays are obviously included here, and we can also deal with keyboards and the few direct digital output transducers, such as the optical shaft position encoder. We will deal with non-digital signals later.

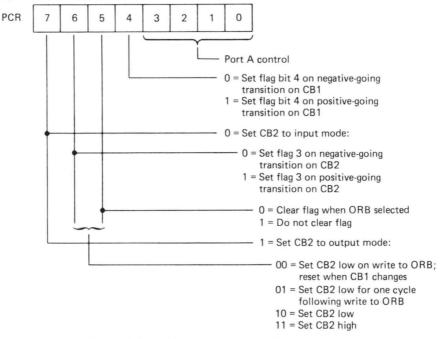

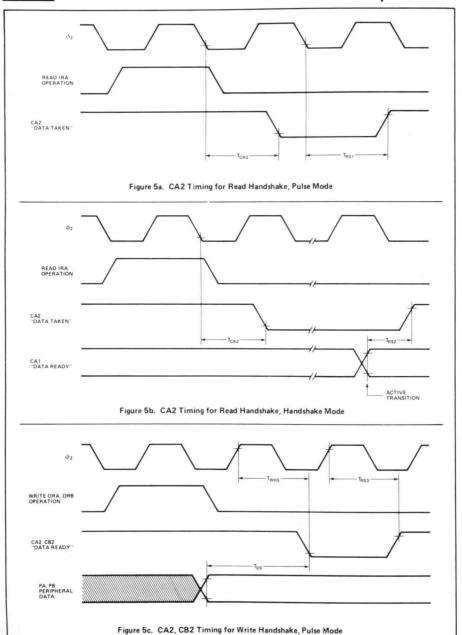

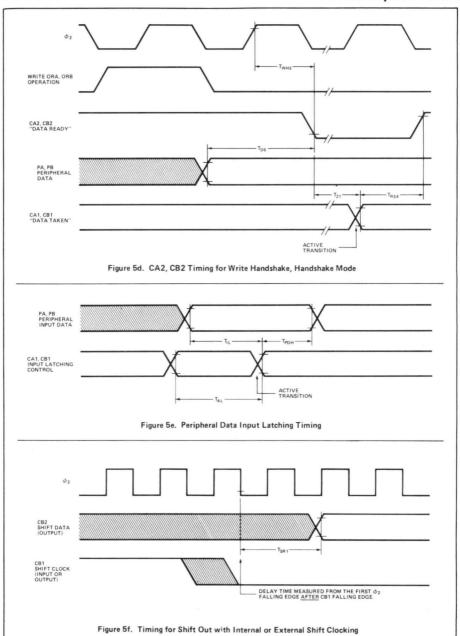

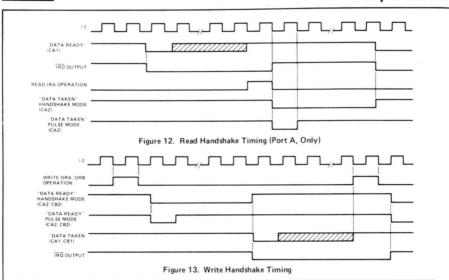

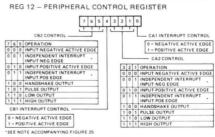

We now use the VIA port in its input mode by setting the data direction register at &FE62 to &00. This means that when we read from &FE60 we read the input register, IRB, and this register can be operated in either the latching mode or the non-latching mode. Latching mode is selected by setting bit 1 of the auxiliary control register (register 11 at &FE6B) to '1'. If it is at '0' we get non-latching mode, and reading from port B reads the values present on the port pins at that time, whereas when operating in latching mode the values read are those that were present when a change of signal occurred on control line CB1. The sense of the change causing the latching can also be programmed, either high to low transition or low to high transition, by setting bit 4 of the peripheral control register (register 12 at &FE6C) to '0' if negative-going latching is required, or to '1' for a positive-going edge.

Since the port is to receive either a '1' or a '0', it might seem that the best arrangement would be to use a change-over switch, as in figure 2.11a. This will

```

/Reserve 31 bytes for assembler at "PROG"

10 DIM PROG 30

/Set port to output mode

20 ?&FE62=255

/&FFF4 will be referred to as OSBYTE

30 OSBYTE=&FFF4

40 FOR I=0 TO 2 STEP 2: P%=PROG

/Set assembler options and

/PC=PROG.

50

COPTI

Start machine

60

. LIGHTS

/code section LIGHTS.

/Setup OSBYTE &97 (151) call

70

LDA #151

80

LDX #&60

/with offset &60

90

LDY &70

/and value to be written

100

JSR OSBYTE

/Call linking routine

110

RTS

120

1

/End of LIGHTS section

130 NEXT

/Repeat with OPT2

140 N=500

/Setup 5 sec. period

150

?&70=&21

/Load R1 G2 code

PROCchange

160

170 N=100

/Setup 1 sec. period

?&70=&32

/Load R1A1 A2 code

180

190

PROCchange

200 N=500

/Setup 5 sec. period

210

?&70=&OC

/Load G1 R2 code

PROCchange

220

/Setup 1 sec. period

230 N=100

240

? & 70 = & 16

/Load A1 R2A2 code

250 PROCchange

260 GOTO 140

/Repeat the cycle

/The CHANGE procedure

270 DEF PROCchange

/calls the LIGHTS routine

280

CALL LIGHTS

/and waits for N/100 seconds

290

TIME=0

300

REPEAT UNTIL TIME > N

310 ENDPROC

/The main program runs from

```

(b)

line 140 through line 260.

Figure 2.10 Traffic light control. (a) Traffic light sequence. (b) Control program

work quite happily, but change-over switches are more expensive than single-throw types and the arrangement of figure 2.11b is just as effective. R is a *pull-up* resistor which ensures that the line to the port is held at logic '1' until the switch is operated.

Figure 2.11 Switch inputs. (a) Change-over switch. (b) Single-throw switch

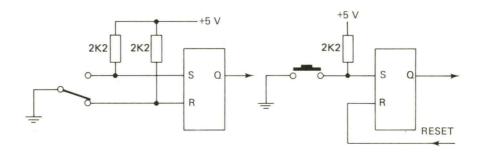

All mechanical switches suffer from bounce of the contacts to a greater or lesser extent, so that as the switch is operated the contacts will make but will not remain in contact at the first attempt. They bounce open again, and may bounce several times before finally resting in contact as intended. This settling period, which may extend over several milliseconds, is of no consequence in some applications, since the computer may not be programmed to check the switch value until the switch has had ample time to settle down. But the computer operates very quickly and in a few milliseconds can carry out several thousand operations, so if it is programmed to check the switch setting at short intervals it may wrongly interpret the bouncing as several independent operations of the switch. To be on the safe side we almost always debounce any switches, either by use of a simple flipflop or by a checking sequence in our program. The use of the flipflop is illustrated in figure 2.12 where the flipflop sets when the switch contacts first come together, and remains set until reset by the return of the switch or the application of a reset signal. The disadvantage of this method is that it requires additional circuitry, though several flipflops suitable for use in this way are packaged together for convenience, as in the SN74LS279 which contains four flipflops. As we are already making use of the computer to sense the setting of the switch,

Figure 2.12 Switch debouncing by use of flipflop

```

10 DIM PROG 500

/Reserve a block of bytes for assembler

20 DIM A(10)

/Reserve array to receive switch numbers

/Define locations of VIA B Timer 1, low byte

30 T1L0=&FE64

Timer 1, high byte

40 T1HI=&FE65

50 ACR=&FE6B

Aux. control reg

Interrupt flg. reg

60 FR=&FE6D

1

70 ?&FE62=0

Data direction reg

80 FOR I=0 TO 2 STEP 2: P%=PROG

90

COPTI

/Start machine code section START

100

. START

LDA &FE60: STA &70 /Read input port and store in &70

110

CMP #0: BEQ START

/If zero, start again

120

/otherwise clear aux. control reg

130 LDA #O: STA ACR

LDA #&88: STA T1L0

/Setup time delay in Timer1

140

150

LDA #&13: STA T1HI

. DELAY

160

170

BIT FR

/Check bit 6 of flag reg. to detect end

BVC DELAY

/of delay and branch back until bit set

180

/Read input port again and compare

190

LDA &FE60

200

CMP &70: BNE START

/with previous value; if not equal

RTS

/start again.

210

220

230 NEXT

/Exit routine with switch values in &70

240 CALL START

250 C=255-?&70 /Complement, so that an ON switch gives a "1"

260 W=0

270 FOR I=0 TO 7

/Find ON switches by ANDing each bit

280

A=2^I

/in turn (referenced as powers of two)

B=A AND C

290

/with the stored value.

Write numbers

300

IF B() O THEN W=W+1: A(W)=I /of ON switches in array A

310 NEXT

320 MODE7

330 IF W=O PRINT TAB(5,6); "SWITCHES ALL OFF" : GOTO 240

340 FOR I=1 TO W

/List ON switches

350 PRINT TAB(5,5+1); "SWITCH ";A(1);" IS ON"

360 NEXT

370 GOTO 240 _____

```

/The main program runs from line 240 through line 370. It makes use of a machine code routine to check for any switch being set, and checks again when Timer1 interval is completed. This is shown by the Overflow flag, which is set by bit6 of the flag register when BIT test is carried out.

Figure 2.13 Debouncing program

however, we normally prefer to use the programmed checking method. The technique is to note when a switch closure is detected and then to check again a certain time later when the bounce has had time to die away. If the switch is still closed we accept that the switch has been operated. The program of figure 2.13 scans eight switches connected to the input port, and uses a time delay of eight milliseconds to allow for the bounce decay.

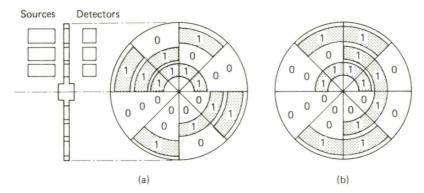

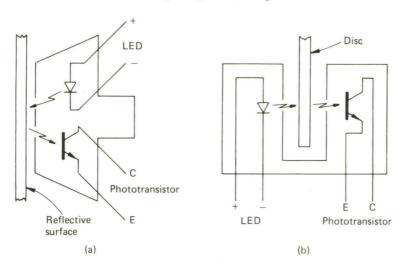

The outputs from an optical shaft position encoder are similar to those from mechanical switches, but being electronic switches they do not suffer from contact bounce. The encoder uses a disc, mounted on the shaft, which has windows laid out in a special pattern, figure 2.14. The output code is generated by optotransistors which detect light from the sources on the other side of the disc if a window happens to lie between. Gray-coded binary, rather than the standard binary, is used to eliminate errors arising from misreading the settings when window edges happen to coincide with the detector and some ambiguous indication could result. With Gray-coded discs no two window edges coincide.

Figure 2.14 Optical shaft position encoder. (a) Binary-coded disc. (b) Gray-coded disc

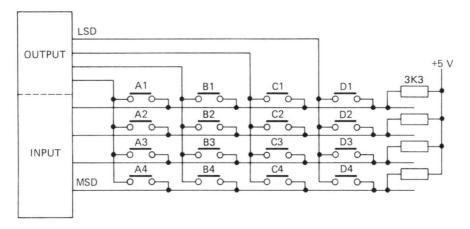

If we have a requirement to input more than eight bits of code, or to scan more than eight switches, we must either provide more input ports or must develop some external selection circuitry to allow us to check successive sets of eight bits. A useful approach is to arrange the switches in a matrix, as in figure 2.15, which is the method widely used in keyboard scanning. Here we use half the port to output a scanning pattern, and the other half to input codes from the matrix which can therefore contain up to sixteen keys. When no key is pressed, the pull-up resistors ensure that the four inputs are all at '1'. The scanning pattern is made up of four bits, only one of which is at '0'. This single '0' is shifted on each succeeding step of the complete scan so that it appears first on the A column of keys, then on the B, then on the C, and so on. After D it reverts to A and the cycle repeats. When a key is pressed, nothing happens until the scanning pattern puts the '0' on the column containing that key. The '0' is then routed through the closed contact to the input bit connected to that row and the computer detects a pressed key. The scanning pattern and inputted code together make up a 'grid reference' for the key. If key B2 is pressed, for example, the input code becomes 1101 when the output pattern is 1011 so the key B2 is defined by the 8-bit code 1101 1011. The character or value indicated by the key is found by using the code as a pointer to a look-up table of character codes, as in the program of figure 2.16a.

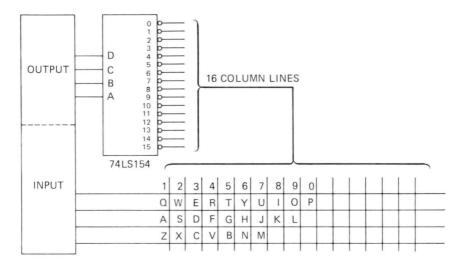

Figure 2.15 Matrix keyboard

A modified method of scanning, making use of the ability to switch the port between input and output modes, is sometimes preferred. The four column bits are first set to output 0000. If a key is pressed, say B2 again, the row input code becomes 1101. This is latched in the port register and the modes are now reversed so that the row connections become outputs, carrying the pattern 1101, and the column connections become inputs. Since switch B2 is still pressed the '0' is connected back to the column inputs to give the pattern 1011, so that the overall 'grid reference' is 1101 1011 as before. The program for this type of scanning is shown in figure 2.16b. Larger keyboard matrices can be dealt with by including extra decoder chips, though the reversing scan method just described cannot then be used. The arrangement in figure 2.17 is capable of dealing with a full 64-key QWERTY-type keyboard.

In discussing the inputting and outputting of data by the computer we have so far assumed that the program routines are entirely under the control of the computer. In other words, it is the computer that initiates all the operations. In checking the keyboard, for example, the scanning sequence is run at regular intervals by the computer, regardless of whether anyone is likely to use the keyboard or not. In simple systems, where the processor is not required to carry out many other tasks, this is perfectly acceptable. Most calculators work on this basis, with the processor idly scanning the keyboard for most of its time waiting for the next key to be pressed. But most systems can make better use of the time available, if they are notified in some way only when a key is pressed, and can ignore the keyboard until then, continuing meanwhile with some other productive program. When a key operation does occur, the running of the existing program must be interrupted until the keyboard scanning operation is completed and then the

```

10 MODE7

20 PRINT TAB(0,0); CHR$(141); "PRESS A KEY ON THE PAD"

30 PRINT TAB(0, 1); CHR$(141); "PRESS A KEY ON THE PAD"

40 DIM PROG 500

/Reserve a block of bytes for assembler

50 OSBYTE=&FFF4

60 FOR I=0 TO 2 STEP 2

70 P%=PROG

COPTI

8D

/Start machine code section START

90

. START

100

LDA #&F:STA &FE62

/Set DDR to give outputs on 4 1sd

LDA #&97:LDX #&60:LDY #7:JSR OSBYTE /and write 0111

110

LDA #&96:LDX #&60:JSR OSBYTE:STY &70

120

/Read port

130

LDA &70:CMP #&F7:BNE FIN

/Branch if key detected

140

LDA #&97:LDX #&60:LDY #&B:JSR OSBYTE/Write next pattern

LDA #&96:LDX #&60:JSR OSBYTE:STY &70

150

/1011 and repeat

LDA &70:CMP #&FB:BNE FIN

160

LDA #&97:LDX #&60:LDY #&D:JSR OSBYTE/Write next pattern

170

LDA #&96:LDX #&60:JSR OSBYTE:STY &70 /1101 and repeat

180

LDA &70:CMP #&FD:BNE FIN

190

200

LDA #&97:LDX #&60:LDY #&E:JSR OSBYTE/Write next pattern

210

LDA #&96:LDX #&60:JSR OSBYTE:STY &70 /1110 and repeat

220

LDA &70:CMP #&FE:BNE FIN

.FIN

230

RTS

240

250

7

260 NEXT I

/Exit routine with value held in &70

270 CALL START

280 IF ?&70=254 GOTO 270/Repeat scan cycle until key detected

290 N=0

300 RESTORE

310 READ A

/Look up value in DATA table

320 IF A=?&70 PROCdisplay:GOTO 270

330 N=N+1

340 IF N)15 PRINT CHR$(7):GOTO 270/Indicate multiple keypress

350 GOTO 310

360 DEF PROCdisplay

370 PRINT TAB(15,10); CHR$(141); N /Print double-height value

PRINT TAB(15, 11); CHR$(141); ~N

380

400 DATA 238, 222, 190, 126, 237, 221, 189, 125, 235, 219, 187, 123, 231

410 DATA 215, 183, 119

```

/The main program runs from line 270 through line 350. The machine code scanning routine is repeated until a depressed key is detected then the value in &70 is used to look up the corresponding character code in a DATA table.

(a)

Figure 2.16 (continued overleaf)

```

10 MODE7

20 PRINT TAB(0,0); CHR$(141); "PRESS A KEY ON THE PAD"

30 PRINT TAB(0,1); CHR$(141); "PRESS A KEY ON THE PAD"

40 DIM PROG 500

/Reserve a block of bytes for assembler

50 OSBYTE=&FFF4

60 FOR I=0 TO 2 STEP 2

70 P%=PROG

80

COPTI

. START

90

100

LDA #&FO:STA &FE62

/Set DDR to give outputs on

LDA #&97:LDX #&60:LDY #&F:JSR OSBYTE /4 msd; write 1111

110

LDA #&96:LDX #&60:JSR OSBYTE:STY &70 /Input pattern and

120

/store 4 1sd at &70

LDA &70:AND #&F:STA &70

130

/Reverse DDR setting and output

140 LDA #&F:STA &FE62

150 LDA #&97:LDX #&60:LDY &70:JSR OSBYTE /returned pattern

LDA #&96:LDX #&60:JSR OSBYTE:STY &70

160

/Store final

170

RTS

/pattern and exit

/routine with value

180

7

190 NEXT I

/held in &70.

200 CALL START

210 IF ?&70=255 GOTO 200/Repeat scan cycle until key detected

220 N=0

230 RESTORE

240 READ A

250 IF A=?&70 PROCdisplay:GOTO 200

260 N=N+1

270 IF N) 15 PRINT CHR$ (7) : GOTO 200

280 GOTO 240

290 DEF PROCdisplay

/DISPLAY procedure

PRINT TAB(15, 10); CHR$(141); ~N

310

PRINT TAB(15, 11); CHR$(141); ~N

320 ENDPROC

330 DATA 238, 222, 190, 126, 237, 221, 189, 125, 235, 219, 187, 123, 231

340 DATA 215, 183, 119

```

/The main program is almost identical to that in figure 2.16a, but the machine code section uses a reversing scan method, changing the DDR setting twice each cycle.

(b)

Figure 2.16 (above and page 33) (a) Program look-up table. (b) Reversing scan pattern

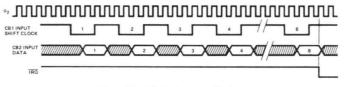

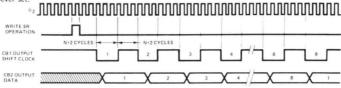

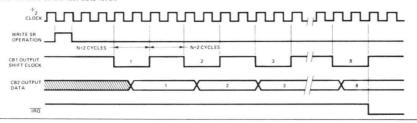

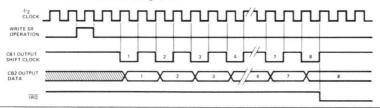

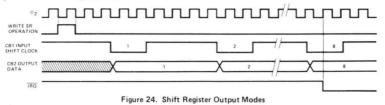

program can be resumed. The same sort of reaction can be incorporated to cover any external interruption. This is exactly the way we operate in real life when we have to interrupt some job that we are doing to answer the telephone or a knock at the door.